#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

## A Practical Oracle for Sequential Code Parallelization

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Computer Science

by

Saturnino Garcia, Jr.

#### Committee in charge:

Professor Michael Taylor, Chair

Professor Peter Asbeck

Professor Chung-Kuan Cheng

Professor Sorin Lerner

Professor Steven Swanson

Copyright

Saturnino Garcia, Jr., 2012

All rights reserved.

| The dissertation of Saturnino Garcia, Jr. is approved,   |

|----------------------------------------------------------|

| and it is acceptable in quality and form for publication |

| on microfilm and electronically:                         |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

| Chair                                                    |

University of California, San Diego

2012

## DEDICATION

To my wife, for her endless love and support.

## EPIGRAPH

## TABLE OF CONTENTS

| Signature P.  | age .    |           |        |       |      |       |       | •                   |      | •    |         | •   |     | •  | • | •  | •   | •  | • |      | iii |

|---------------|----------|-----------|--------|-------|------|-------|-------|---------------------|------|------|---------|-----|-----|----|---|----|-----|----|---|------|-----|

| Dedication .  |          |           |        |       |      |       |       |                     |      |      |         |     |     |    |   |    |     |    |   |      | iv  |

| Epigraph .    |          |           |        |       |      |       |       |                     |      |      |         |     |     |    | • |    |     |    |   |      | V   |

| Table of Cor  | ntents   |           |        |       |      |       |       |                     |      |      |         |     |     |    |   |    |     |    |   |      | vi  |

| List of Figur | res .    |           |        |       |      |       |       |                     |      |      |         |     |     |    | • |    |     |    |   |      | ix  |

| List of Table | es       |           |        |       |      |       |       |                     |      |      |         |     |     |    | • |    |     |    |   | <br> | Х   |

| Acknowledg    | ements   | s         |        |       |      |       |       |                     |      |      |         |     |     |    | • |    |     |    |   |      | xi  |

| Vita and Pu   | ıblicati | ions .    |        |       |      |       |       |                     |      |      |         |     |     |    |   |    |     |    |   |      | xiv |

| Abstract of   | the Di   | issertati | on .   |       |      |       |       |                     |      | •    |         |     |     |    |   |    |     |    |   |      | xvi |

| Chapter 1     | Intro    | oduction  | 1      |       |      |       |       |                     |      |      |         |     |     |    |   |    |     |    |   |      |     |

|               | 1.1      | Taxon     | omy o  | of Pa | aral | lleli | zat   | ion                 | To   | ool  | S .     |     |     |    |   |    |     |    |   |      | 3   |

|               |          | 1.1.1     | Over   | viev  | w o  | f Pa  | ara   | lleli               | zat  | tion | ı S     | tag | ges |    |   |    |     |    |   |      | 4   |

|               |          | 1.1.2     | Exis   | ting  | Pa   | ral   | leliz | zati                | on   | To   | ools    | 3   |     |    |   |    |     |    |   |      | 5   |

|               | 1.2      | A Prae    | ctical | Ora   | acle | for   | Pa    | aral                | leli | iza  | tio     | n   |     |    |   |    |     |    |   |      | 7   |

|               | 1.3      | Thesis    | Orga   | niza  | atio | n.    |       |                     |      |      |         |     |     |    |   |    |     |    |   |      | 9   |

| Chapter 2     |          | Cost of   |        |       |      |       |       |                     |      |      |         |     |     |    |   |    |     |    |   |      |     |

|               | 2.1      | Examp     |        |       |      |       |       |                     |      |      | _       | •   |     |    |   |    |     |    |   |      |     |

|               | 2.2      | User S    |        |       |      |       |       |                     |      |      |         |     |     |    |   |    |     |    |   |      |     |

|               |          | 2.2.1     | Setu   |       |      |       |       |                     |      |      |         |     |     |    |   |    |     |    |   |      |     |

|               |          | 2.2.2     | Benc   |       |      |       |       |                     |      |      |         |     |     |    |   |    |     |    |   |      |     |

|               |          | 2.2.3     | Impa   |       |      |       | _     |                     |      |      |         |     |     |    |   |    |     |    |   |      |     |

|               |          | 2.2.4     | Time   | _     |      |       |       |                     |      |      | _       |     |     |    |   |    |     |    |   |      |     |

|               |          | 2.2.5     | Thre   | ats   | to   | Val   | idit  | У                   |      |      |         |     |     |    |   |    |     |    |   |      | 22  |

|               |          | 2.2.6     | Cond   | clusi | ions | 8.    |       |                     |      |      |         |     |     | •  | • | •  | •   |    |   |      | 23  |

| Chapter 3     | Syst     | em Ove    | rview  |       |      |       |       |                     |      |      |         |     |     |    |   |    |     |    |   |      | 26  |

|               | 3.1      | Usage     | Mode   | el.   |      |       |       |                     |      |      |         |     |     |    |   |    |     |    |   |      | 26  |

|               | 3.2      | Systen    |        |       |      |       |       |                     |      |      |         |     |     |    |   |    |     |    |   |      |     |

|               | 3.3      | Limita    | tions  | of I  | Krei | mli   | n a   | $\operatorname{nd}$ | oth  | ner  | $D_{i}$ | yna | am  | ic | A | na | ιly | se | S |      | 33  |

| Chapter 4 | Plan | ning-Aware Parallelism Discovery                     | 35  |

|-----------|------|------------------------------------------------------|-----|

|           | 4.1  | Requirements of Planning-Aware Discovery             |     |

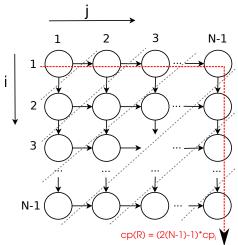

|           | 4.2  | Background: Critical Path Analysis                   |     |

|           | 4.3  | Hierarchical Critical Path Analysis                  | 38  |

|           |      | 4.3.1 Defining a Region                              | 39  |

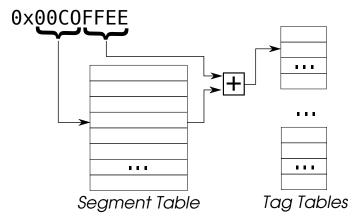

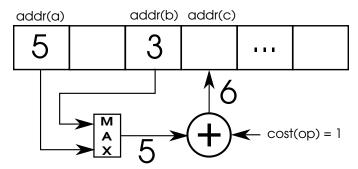

|           |      | 4.3.2 Calculating Critical Path with Shadow Memory . | 41  |

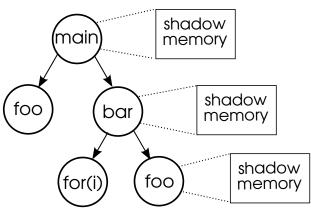

|           |      | 4.3.3 Introducing Hierarchy into Shadow Memory       | 44  |

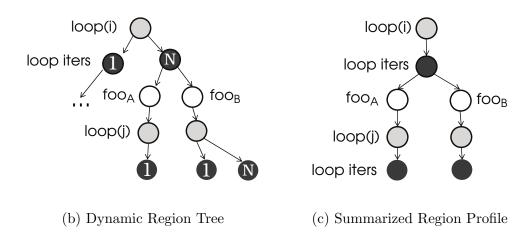

|           |      | 4.3.4 Summarizing Dynamic Regions                    | 47  |

|           | 4.4  | Identifying Local Parallelism                        | 48  |

|           |      | 4.4.1 Initial Approach: Parallelism Charts           | 49  |

|           |      | 4.4.2 Self-Parallelism                               | 51  |

|           | 4.5  | Evaluation                                           | 57  |

| Chapter 5 | Fron | n Parallelism to Parallelization Plan                | 62  |

|           | 5.1  | Defining Parallelism Planning                        | 62  |

|           | 5.2  | Estimating Parallel Execution Time                   | 64  |

|           | 5.3  | Identifying Parallelism Types                        | 66  |

|           | 5.4  | Planner Personalities                                | 67  |

|           |      | 5.4.1 OpenMP Planning Personality                    | 68  |

|           |      | 5.4.2 OpenCL Planning Personality                    | 70  |

|           |      | 5.4.3 Cilk++ Planning Personality                    | 72  |

|           |      | 5.4.4 Developing Additional Planner Personalities    | 73  |

|           | 5.5  | Experimental Evaluation                              | 74  |

|           |      | 5.5.1 Methodology                                    | 75  |

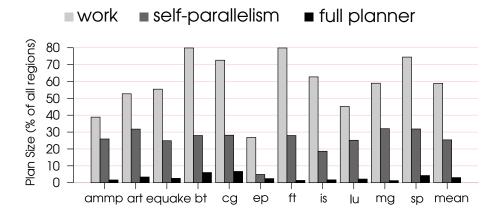

|           |      | 5.5.2 Comparing Plan Size                            | 76  |

|           |      | 5.5.3 Performance Comparison                         | 77  |

|           |      | 5.5.4 Effectiveness of Region Prioritization         | 79  |

|           |      | 5.5.5 Influences on Plan Size                        | 80  |

|           |      | 5.5.6 Initial GPGPU Planning Results                 | 81  |

| Chapter 6 | _    | roving Kremlin's Practicality                        |     |

|           |      | Efficient Shadow Memory Organization                 |     |

|           | 6.2  | Static Partial Evaluation of CPA                     | 91  |

|           | 6.3  | Evaluation                                           | 94  |

|           |      | 6.3.1 Shadow Memory Optimization                     | 95  |

|           |      | 6.3.2 Static Partial Evaluation of CPA               | 98  |

| Chapter 7 | Rela | ted Work                                             | 100 |

|           | 7.1  | Parallelism Discovery                                | 100 |

|           | 7.2  | Parallelism Planning                                 | 102 |

|           | 7.3  | Performance Prediction                               | 103 |

|           | 7.4  | Shadow Memory Design                                 |     |

|           | 7.5  | Parallel Performance Debugging Tools                 | 106 |

| Chapter 8    | Summary |  |  | • |  |  |  |  |  | • | • | • | • | • | • | • | • | • |  | 108 |

|--------------|---------|--|--|---|--|--|--|--|--|---|---|---|---|---|---|---|---|---|--|-----|

| Bibliography |         |  |  |   |  |  |  |  |  |   |   |   |   |   |   |   |   |   |  | 112 |

## LIST OF FIGURES

| Figure 1.1:  | A Taxonomy of Parallelization Tools                              | 4  |

|--------------|------------------------------------------------------------------|----|

| Figure 2.1:  | Speedup vs. Time Graphs for All Users (sift)                     | 20 |

| Figure 3.1:  | Kremlin's Usage Model                                            | 27 |

| Figure 3.2:  | Overview of the Kremlin System Architecture                      | 30 |

| Figure 4.1:  | Localizing Parallelism                                           | 37 |

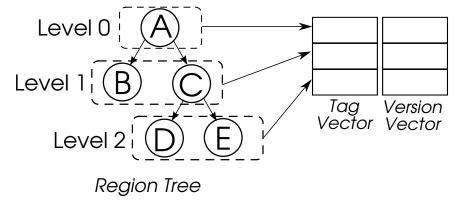

| Figure 4.2:  | HCPA Hierarchical Region Model and Summarization                 | 40 |

| Figure 4.3:  | Traditional Shadow Memory Organization                           | 41 |

| Figure 4.4:  | Calculating Parallel Time with Shadow Memory                     | 42 |

| Figure 4.5:  | Shadow Memory and Region Hierarchy                               | 44 |

| Figure 4.6:  | Level-based Sharing of Shadow Memory Tags                        | 46 |

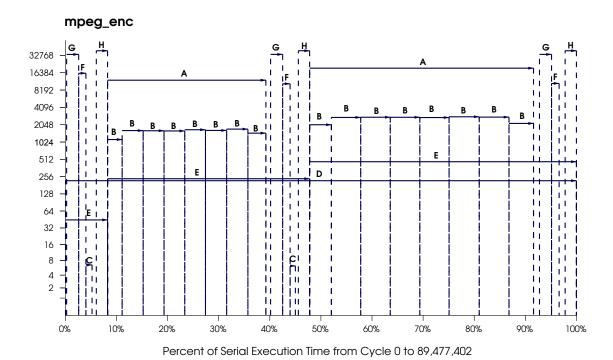

| Figure 4.7:  | Parallelism Chart for MPEG Encoder                               | 50 |

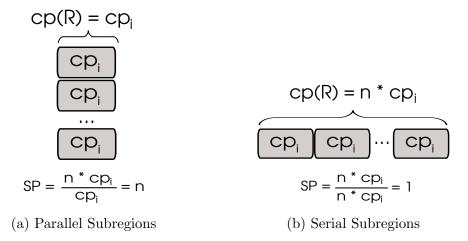

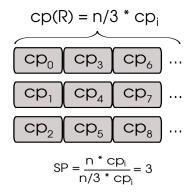

| Figure 4.8:  | Self-Parallelism Scenarios                                       | 54 |

| Figure 4.9:  | Self-Parallelism with Pipeline Parallelism                       | 55 |

| Figure 4.10: | Uncovering Hidden Parallelism with Self-Parallelism              | 56 |

| Figure 4.11: | Classification of Regions Based on Total- and Self-Parallelism . | 58 |

| Figure 4.12: | Percentage of Regions Parallelized as a Function of Parallelism  |    |

|              | and Work                                                         | 59 |

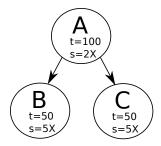

| Figure 5.1:  | Shortcomings of Greedy Planning                                  | 69 |

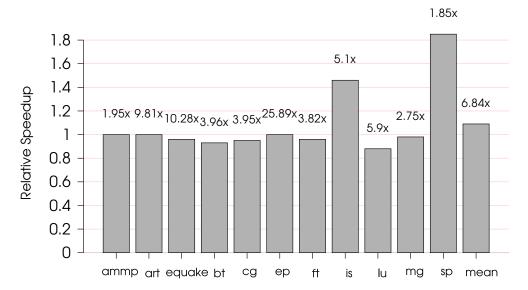

| Figure 5.2:  | Evaluating the Performance of Kremlin-based Parallelization      | 77 |

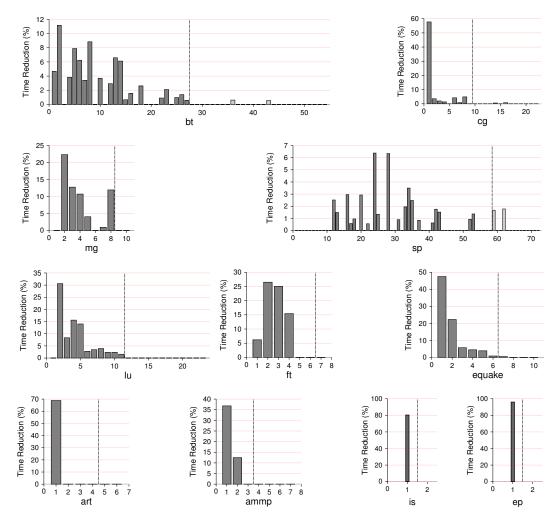

| Figure 5.3:  | Effectiveness of Region Prioritization                           | 78 |

| Figure 5.4:  | Effects of Factors on Plan Size                                  | 81 |

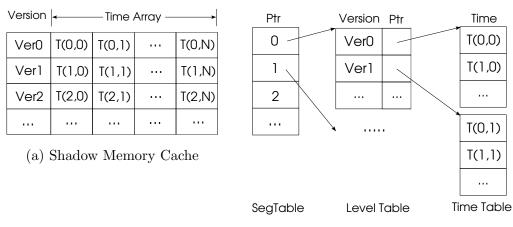

| Figure 6.1:  | Efficient Shadow Memory Organization                             | 87 |

| Figure 6.2:  | Exploring Optimization Possibilities                             | 91 |

## LIST OF TABLES

| Table 1.1: | Auto-Parallelization Performance                                                    | 5  |

|------------|-------------------------------------------------------------------------------------|----|

| Table 2.2: | Speedup and Recommendation Rank of Critical Regions Speedup Achieved and Time Spent | 19 |

| Table 4.1: | Region Key for MPEG Encoder Benchmark                                               | 49 |

| Table 5.2: | Evaluating Plan Size                                                                | 80 |

| Table 6.2: | Shadow Memory Overheads for HCPA                                                    | 95 |

|            | Performance Impact of Optimized Shadow Memory                                       |    |

#### **ACKNOWLEDGEMENTS**

This thesis would not have been possible if not for the support of a great many people. My advisor, Michael Taylor, provided invaluable feedback on my research and created an environment that allowed me to blossom as a researcher. His advice allowed me to keep the proper perspective on research and life through the inevitable ups and downs of my studies.

Others have also provided me great guidance—both formal and informal—during my career. In particular, I would like to thank the following people for their advisory roles: the members of my thesis committee; my former advisor, Alex Orailoglu; and my undergraduate advisors at Drexel University, Moshe Kam and Kapil Dandekar.

The work presented in this thesis was a close collaboration with several highly talented individuals. I am especially thankful to my colleague and friend, Donghwan Jeon, with whom I enjoyed many a delightful conversation. I would also like to acknowledge the hard work and intelligence of Chris Louie, who I was lucky enough to mentor over several years. Of course, I would be remiss if I did not acknowledge the valuable feedback received from my current and former officemates as well as the members of the architecture and programming systems groups here at UCSD.

Finally, I offer my heartfelt thanks to my family for their unwavering belief in me. Throughout my life they have always encouraged and supported me while I have pursued my dreams, however crazy they may have seemed.

Chapters 1, 2, 3, 4, 5, and 7 contain material from "Kremlin: Rethinking and Rebooting gprof for the Multicore Age", by Saturnino Garcia, Donghwan Jeon, Chris Louie, and Michael Bedford Taylor, which appears in *PLDI '11: Proceedings of the 32nd ACM SIGPLAN conference on Programming language design and implementation*. The dissertation author was the primary investigator and author of this paper. The material in these chapters is copyright ©2011 by the Association for Computing Machinery, Inc.(ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or commercial advantage and

that copies bear this notice and the full citation on the first page in print or the first screen in digital media. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or email permissions@acm.org.

Chapters 4, 5, and 7 contain material from "Kismet: parallel speedup estimates for serial programs", by Donghwan Jeon, Saturnino Garcia, Chris Louie, and Michael Bedford Taylor, which appears in OOPSLA '11: Proceedings of the 2011 ACM international conference on Object oriented programming systems lanquages and applications. The dissertation author was the secondary investigator and author of this paper. The material in these chapters is copyright ©2011 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page in print or the first screen in digital media. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or email permissions@acm.org.

Chapters 4 and 5 contain material from "The Kremlin Oracle for Sequential Code Parallelization", by Saturnino Garcia, Donghwan Jeon, Chris Louie, and Michael Bedford Taylor, which is set to appear in *IEEE Micro*. The dissertation author was the primary investigator and author of this paper. The material in this chapter is copyright ©2012 by the Institute of Electrical and Electronics Engineers (IEEE). Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any

copyrighted component of this work in other works.

Chapter 4 contains material from "Bridging the Parallelization Gap: Automating Parallelism Discovery and Planning", by Saturnino Garcia, Donghwan Jeon, Chris Louie, Srivanthi Kota-Venkata, and Michael Bedford Taylor, which appears in *USENIX Workshop on Hot Topics in Parallelism (HotPar)*, 2010. The dissertation author was the primary investigator and author of this paper.

#### VITA

| 2005           | B. S. in Computer Engineering<br>Drexel University<br>Philadelphia, Pennsylvania |

|----------------|----------------------------------------------------------------------------------|

| 2005-2012      | Graduate Research Assistant<br>University of California, San Diego               |

| 2006-2008,2011 | Teaching Assistant<br>University of California, San Diego                        |

| 2007           | M. S. in Computer Science<br>University of California, San Diego                 |

| 2011           | Instructor<br>University of California, San Diego                                |

| 2011-2012      | Master Teaching Assistant<br>University of California, San Diego                 |

| 2012           | Ph. D. in Computer Science                                                       |

#### **PUBLICATIONS**

University of California, San Diego

Saturnino Garcia, Donghwan Jeon, Chris Louie, Michael Bedford Taylor, "The Kremlin Oracle for Sequential Code Parallelization", *IEEE Micro*, *To appear*.

Donghwan Jeon, Saturnino Garcia, Chris Louie, Michael Bedford Taylor, "Kismet: Parallel Speedup Estimates for Serial Programs", Proceedings of ACM Conference on Object Oriented Programming Systems Languages and Applications (OOPSLA), October 2011.

Saturnino Garcia, Donghwan Jeon, Chris Louie, Michael Bedford Taylor, "Kremlin: Rethinking and Rebooting gprof for the Multicore Age", *Proceedings of ACM SIGPLAN Conference on Programming Language Design and Implementation (PLDI)*, June 2011.

Donghwan Jeon, Saturnino Garcia, Chris Louie, Michael Bedford Taylor, "Parkour: Parallel Speedup Estimates for Serial Programs", *USENIX Workshop on Hot Topics in Parallelism (HotPar)*, May 2011.

Nathan Goulding, Jack Sampson, Ganesh Venkatesh, Saturnino Garcia, Joe Aurricchio, Po-Chao Huang, Manish Arora, Siddharth Nath, Vikram Bhatt, Jonathan Babb, Steven Swanson, Michael Bedford Taylor, "The GreenDroid mobile application processor: An architecture for silicons dark future", *IEEE Micro*, March/April 2011.

Saturnino Garcia, Donghwan Jeon, Chris Louie, Sravanthi Kota Venkata, Michael Bedford Taylor, "Kremlin: Like gprof but for Parallelization", *Proceedings of ACM Symposium on Principles and Practice of Parallel Programming (PPoPP)*, February 2011.

Jack Sampson, Ganesh Venkatesh, Nathan Goulding, Saturnino Garcia, Steven Swanson, Michael Bedford Taylor, "Efficient complex operators for irregular code", Proceedings of the International Symposium on High-Performance Computer Architecture (HPCA), February 2011.

Saturnino Garcia, Donghwan Jeon, Chris Louie, Sravanthi Kota Venkata, Michael Bedford Taylor, "Bridging the Parallelization Gap: Automating Parallelism Discovery and Planning", *USENIX Workshop on Hot Topics in Parallelism (HotPar)*, June 2010.

Ganesh Venkatesh, Jack Sampson, Nathan Goulding, Saturnino Garcia, Vladyslav Bryksin, Jose Lugo-Martinez, Steven Swanson, Michael Bedford Taylor, "Conservation Cores: Reducing the Energy of Mature Computations", *Proceedings of the Fifteenth International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS)*, March 2010.

Sravanthi Kota Venkata, Ikkjin Ahn, Donghwan Jeon, Anshuman Gupta, Chris Louie, Saturnino Garcia, Serge Belongie, Michael Bedford Taylor, "SD-VBS: The San Diego Vision Benchmark Suite", *Proceedings of IEEE International Symposium on Workload Characteristics (IISWC)* October 2009.

Saturnino Garcia, Alex Orailoglu, "Making DNA Self-Assembly Error Proof: Attaining Small Growth Error Rates Through Embedded Information Redundancy", Proceedings of Design, Automation, and Test in Europe Conference & Exhibition (DATE), April 2009.

Saturnino Garcia, Alex Orailoglu, "Online Test and Fault-Tolerance for Nanoelectronic Programmable Logic Arrays", *Proceedings of the International Symposium on Nanoelectronic Architectures (NANOARCH)*, June 2008.

Gustave Anderson, Leonardo Urbano, Gaurav Naik, David Dorsey, Andrew Mroczkowski, Donovan Artz, Nicholas Morizio, Andrew Burnheimer, Kris Malfettone, Dan Lapadat, Evan Sultanik, Saturnino Garcia, Max Peysakhov, William Regli, Moshe Kam, "A Secure Wireless Agent-based Testbed", *Proceedings of IEEE International Information Assurance Workshop (IWIA)*, April 2004.

#### ABSTRACT OF THE DISSERTATION

#### A Practical Oracle for Sequential Code Parallelization

by

Saturnino Garcia, Jr.

Doctor of Philosophy in Computer Science

University of California, San Diego, 2012

Professor Michael Taylor, Chair

With the relatively recent switch from single- to multi-core processors, parallelism now plays a much larger role in maximizing program performance. This switch calls for converting the existing serial implementations of programs into parallel implementations in order to ensure scalable performance on future generations of processors. While automated tools to perform this conversion have been developed, the resulting performance often significantly lags behind that of manually parallelized code. This gap in performance has led researchers to develop tools that ease the manual parallelization process. These tools have greatly simplified the later stages of parallelization, but they provide no assistance with one of the primary questions faced by programmers: "Which parts of this program should I spend time parallelizing?".

In this dissertation we examine the design and implementation of Kremlin, a practical oracle for the parallelization of sequential programs. Kremlin predicts the outcomes of parallelization in order to guide the programmer towards regions of the program that will be most fruitful for parallelization. Kremlin accomplishes this task by extending a classic technique, critical path analysis, to make it practical for

two often-overlooked phases of parallelization: parallelism discovery and planning. This oracle requires only unmodified serial source code, a representative set of inputs, and simple system parameters such as the number of cores to produce a parallelization plan that prioritizes regions by their potential parallel speedup. Our results highlight Kremlin's utility as a practical oracle: parallelization guided by Kremlin results in fewer program regions being parallelized  $(1.57\times, on average)$  in order to achieve peak parallel performance.

# Chapter 1

## Introduction

The emergence of multi-core processors over the past decade has been a disruptive force in software engineering. For a half century before the switch to multi-core, software engineers benefited from a stable hardware interface that presented the abstraction of a single processing core. The single-core abstraction was not the only abstraction available to programmers but it has been the dominant one; abstractions for multiprocessors (e.g. simultaneous multiprocessing) have a long history but were largely ignored by mainstream software engineers as multiprocessor systems have until recently been the exception rather than the rule.

The abstraction of a single core processor hid many of the changes made to computer architecture during this time. This has allowed software engineers to see exponential increases in the performance of their programs as new processors were developed—all without any changes to their code. While multi-core processors support the single-core abstraction, the free lunch appears to be over: software engineers can continue to write code as they always did but the performance of this code will no longer see exponential improvements from generation to generation.

Much of the performance available in multi-core processors is tied to the abundance of available hardware parallelism. Computer architects continue to look for ways to use this hardware parallelism to benefit single-thread programs [KST10, KLW<sup>+</sup>04, TT11], but unlocking the full potential of hardware parallelism will require the use of software parallelism.

Software parallelism comes in many forms, both within a program and

across multiple programs. Parallelism across programs requires little from programmers but is limited in its utility: in many contexts the number of concurrent, active programs is limited, placing an upper bound on the number of cores that are useful. This type of parallelism also does not provide scalable performance, only attempting to minimize the performance degradation that occurs when multiple programs are concurrently executing. Far more important for scalable performance is the other type of parallelism, that which comes from within the program itself.

Parallel programming has a rich history, but the scarcity of multiprocessor systems has limited parallel programming to a small number of domains, e.g. scientific computing. Parallel programming has gained a reputation as being extremely difficult, which is understandable given the difficulties humans have with thinking about multiple concurrent events: humans are notoriously poor multitaskers. Parallel programming requires a unique set of skills, which a vast majority of programmers have largely ignored as decades of exponential improvements in single-threaded performance have minimized their importance. The rise of multicore processors has changed this equation, forcing mainstream programmers to question how to exploit the parallelism that may be present in their existing serial programs.

Automatic parallelizing compilers such **Polaris**  $[BDE^{+}02],$ SUIF [HAA+96], and RawCC [LBF+98] offer a fully automated approach to program parallelization. These approaches are obviously desirable for software engineers but the performance of the code they generate often pales in comparison to the code generated by a skilled human. These fully automated tools are hampered by the ambiguity that arises from a lack of semantic information during static analysis. This lack of information forces these compilers to be conservative in order to maintain program correctness. Researchers have looked at the possibility of allowing the programmers to annotate programs with semantic information but these approaches include a large, possibly non-trivial manual component and have not seen widespread adoption by software engineers.

Programmers who wish to obtain maximum parallel performance have little recourse other than manual parallelization. With this situation in mind there has been a push to develop tools to aid in manual parallelization. One area that has seen notable success is this regard is the development of language extensions or parallel libraries. OpenMP [DM98] and Cilk++ [Lei09] are two examples. Both of these language additions make it trivial to express parallelism in many instances, requiring the addition of only a single line of code in some cases. These approaches have the potential to increase programmer productivity when moving from earlier, low-level approaches such as pthreads in much the same way that moving from assembly languages to high-level programming languages increased productivity in the 1950's and 60's.

Researchers have also developed tools to help the parallel programmer debug both the correctness and performance [TMC09, HLL10, AL90] of their parallel programs. While all of these tools are of assistance to software engineers, they do not form a complete picture of the parallelization process. These tools rely on the basic assumption that programmers have knowledge of which parts of the program have parallelism and should be parallelized. These are non-trivial tasks, even for moderately-sized software projects. What are needed are tools to help the programmer with these critical but often overlooked aspects of parallelization.

In the following section, we will discuss a taxonomy of parallelization tools that we developed to illuminate the end-to-end parallelization process and to identify weaknesses in the existing set of tools. The insights gained from creating this taxonomy led us to the creation of Kremlin, a practical oracle for the parallelization of sequential programs. This oracle predicts the outcome of parallelization, providing guidance to the programmer during the initial phases of parallelization.

## 1.1 Taxonomy of Parallelization Tools

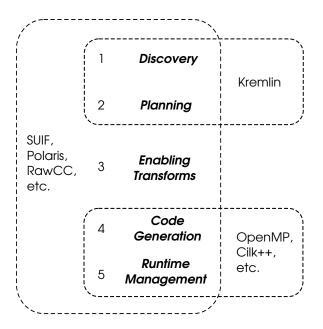

Figure 1.1 presents our taxonomy for parallelization tools. This taxonomy contains five basic phases that are needed to convert the serial implementation of a program into a parallel implementation.

Figure 1.1: **A Taxonomy of Parallelization Tools.** The taxonomy categorizes parallelization tools based on which of five fundamental parallelization stages they assist with. Automatic parallelizing compilers like Polaris [BDE<sup>+</sup>02] and SUIF [HAA<sup>+</sup>96] attempt to perform all five without programmer assistance, while tools like OpenMP, Cilk++ [Lei09], and X10 [SSvP07] focus on the last two. We have developed Kremlin, a tool that focus on the first two stages.

## 1.1.1 Overview of Parallelization Stages

Parallelization starts with *Parallelism Discovery* where the program is inspected to determine which of its regions contains parallelism. Parallelism comes in many forms, not all of which will be exploitable on any given system. This stage must therefore also be capable of distinguishing between different types of parallelism so as to give a more accurate picture of the program's potential. The second stage is that of *Parallelism Planning*, which is where decisions must be made regarding which regions of the program should be parallelized. Planning for an ideal system is trivial: simply parallelize every region that has parallelism, prioritizing those regions with a combination of high coverage and high parallelism. Planning for real systems is unfortunately non-trivial. The planner must account for the exploitability of specific types of parallelism, limitations on the amount of parallel resources available, and overhead introduced from parallelization. The third stage

Table 1.1: **Auto-Parallelization Performance.** For the Rodinia [CBM<sup>+</sup>09] benchmark suite, Intel's icc compiler successfully auto-parallelized only 17% of the program regions that were parallelized by humans despite the relative simplicity of the benchmarks. Further analysis revealed that over half of the regions were not auto-parallelized because of dependencies that could not be resolved statically, a key limitation of parallelizing compilers.

| Benchmark      | Parallelized (Human) | Parallelized (icc) | Success Rate (icc) |

|----------------|----------------------|--------------------|--------------------|

|                | ,                    | ,                  | , ,                |

| backprop       | 2                    | 0                  | 0%                 |

| bfs            | 2                    | 0                  | 0%                 |

| heartwall      | 1                    | 0                  | 0%                 |

| hotspot        | 2                    | 1                  | 50%                |

| kmeans         | 1                    | 0                  | 0%                 |

| lavaMD         | 1                    | 0                  | 0%                 |

| lud            | 2                    | 0                  | 0%                 |

| nn             | 1                    | 0                  | 0%                 |

| nw             | 2                    | 0                  | 0%                 |

| pathfinder     | 1                    | 0                  | 0%                 |

| particlefilter | 10                   | 2                  | 20%                |

| srad           | 2                    | 2                  | 100%               |

| streamcluster  | 2                    | 0                  | 0%                 |

| Total          | 29                   | 5                  | 17%                |

in our taxonomy is *Enabling Transforms*. This stage involves transforming the program to exploit the parallelism that was detected in the first stage. The transforms required here vary widely in their complexity; the simplest cases require only privatizing some variable or arrays while more complex cases may require intricate transformations such as loop skewing and interchange. The final two stages of parallelization, *Code Generation* and *Runtime Management*, deal with generating parallel code and providing the runtime environment in which the parallelism is exploited with minimal overhead.

## 1.1.2 Existing Parallelization Tools

Fully Automated Tools As shown in Figure 1.1, automatic parallelizing compilers such as Polaris [BDE<sup>+</sup>02], SUIF [HAA<sup>+</sup>96], and RawCC [LBF<sup>+</sup>98] attempt

to automate all stages of our taxonomy. This approach eliminates the need for programmers to modify their programs, but it often results in performance that pales in comparison to manual approaches.

Parallelizing compilers have the onus of ensuring correctness so they must prove the safety of any transforms they perform, mainly using only static program analysis. Proving correctness is not possible in many cases without the benefit of additional runtime or semantic information to resolve ambiguities. Table 1.1 demonstrates the difficulty a state-of-the-art parallelizing compiler, icc, has in proving the safety of even simple transformations. icc could parallelize only 17% of the regions that were manually parallelized despite all required program transformations having already been manually performed. Our analysis revealed that over 50% of the regions failed to be parallelized because icc could not statically resolve potential dependencies. Tournavitis et al [TWFO09] also demonstrated the poor performance of icc on the generally high-parallelism benchmarks in NPB [BBB+91].

Programmer-Oriented Tools The often lackluster performance of these completely automated approaches has given rise to an alternative approach, one centered around providing automated tools focusing on specific parts of the taxonomy. As previously mentioned, tools such as OpenMP, Cilk++ [Lei09], X10 [SSvP07], and Fast Track [KBDZ09] have greatly eased the process of indicating parallel regions of the code. These tools correspond to the final two stages of our taxonomy. Researchers have spent considerably less time on tools for the first three stages. While some tools have been developed for automating the enabling transforms stage [DME09, WST09], this stage is the most difficult and benefits most from manual intervention. It is therefore of little surprise that few tools have been developed for this stage; what is surprising is the lack of tools for the first two stages, discovery and planning.

Existing tools for parallelism discovery tend to rely either on critical path analysis (CPA) [Kum88, HSHZ09, RVVYS10] or on dependence testing [Lar93, ZNJ09, KKL10], both of which are poorly suited as precursors for parallelism planning. CPA is useful for quantifying the amount of parallelism within a program but

is overly optimistic, leading to inaccurate estimates of the potential speedup from parallelization. CPA also looks only at the program as a whole, severely limiting its utility in quantifying the impact of parallelizing only parts of the program. Dependence testing reports which regions can be executed concurrently but is closely tied to program structure, leading latent parallelism to go unreported. Dependence testing also does not quantify parallelism, making it difficult to estimate parallel speedup in all but the most trivial cases.

Parallelism planning has largely been overlooked by the research community. While automatic parallelizing compilers implicitly do planning, their planning algorithms are generally not applicable to programmer-oriented planning. As previously discussed, planning is a non-trivial task that must take into account many complex, interacting factors. Without automated tools for this task, programmers are often forced into an *ad hoc* planning methodology that reduces their productivity and can lead to suboptimal parallel performance.

## 1.2 A Practical Oracle for Parallelization

Software engineers must confront the following question at the very beginning of parallelization: "What parts of the program should I spend time parallelizing?". Answering this question manually often requires years of parallel programming experience in addition to a detailed understanding of the program's code structure and dependencies. Neither of these are easy to come by so programmers are forced to consult one or more tools for guidance.

Programmers attempt to act as *seers*, interpreting the results of existing tools to determine a plan for parallelization. Unfortunately, these tools offer mostly vague or misleading guidance. The confusing nature of these tools' results springs from a number of sources. First, these tools may have incomplete knowledge of parallelization. For example, programmers often repurpose serial profilers (e.g gprof) for parallelization planning, despite the fact that high coverage does not correlate with high parallelism. Second, these tools may guide programmers down dead-end paths or fail to alert them of important opportunities. For example, pro-

grammers consulting critical path analysis (CPA) or dependence testing tools are likely to waste time on serial regions or to ignore parallel regions masked by serial implementations. Finally, these tools may lack sufficient foresight. For example, tools that rely on greedy algorithms to select regions to parallelize may suggest a parallelization whose benefit is later negated by another suggested parallelization.

Instead of forcing programmers to act as seers, we should aim to provide them with a tool that acts as a parallelization oracle. We have designed Kremlin to meet this goal, and act as a practical oracle for parallelization of sequential programs. As a parallelization oracle Kremlin predicts the extraordinarily complex outcomes of parallelization with uncanny precision, offering its users an ordered parallelization plan to guide them through the regions of the program they should parallelize. Unlike other tools, Kremlin is a practical tool for parallelization: Kremlin makes its predictions using only serial source code, a sample input, and a simple description of the target platform.

Kremlin builds upon critical path analysis, but introduces several novel techniques to make CPA suitable as a basis for a practical oracle: a new type of dynamic program analysis called *hierarchical critical path analysis* (HCPA); the concept of *self-parallelism*; a lightweight method for approximating self-parallelism; and the concept of a *planning personality* that tailors a parallelization plan to a specific target system. These contributions will be discussed in detail throughout the rest of this dissertation.

Kremlin has shown to be effective at reducing the number of program regions that need to be parallelized, with its recommendations leading to an average  $1.57\times$  fewer parallelized regions when compared to an expert, third-party implementation. This reduction in regions comes with little-to-no impact on performance compared to the third-party implementation, and in several cases greatly exceeds third-party performance. Results also show that Kremlin accurately orders region recommendations, with an average of 86.4% of the total parallel speedup available after completing only the first half of recommendations.

## 1.3 Thesis Organization

The rest of this thesis will have the following organization. In Chapter 2 we will examine the ineffective parallelization methodology that many programmers employ today. This chapter will also present the results of a user study that we performed to quantify the cost of inefficient parallelism planning. This user study used an early prototype of Kremlin; we will discuss how the results of this study helped shape the direction of Kremlin as a practical oracle.

In Chapter 3 we will look at Kremlin's usage model and present a high-level system overview. This overview will tie together Kremlin's individual components, which will be described in further detail in the subsequent chapters.

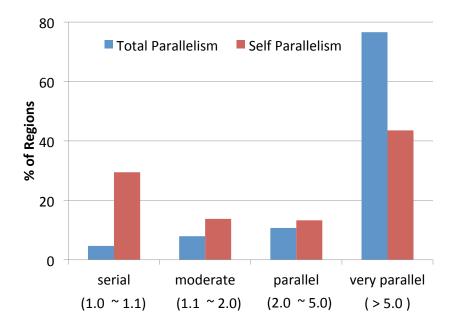

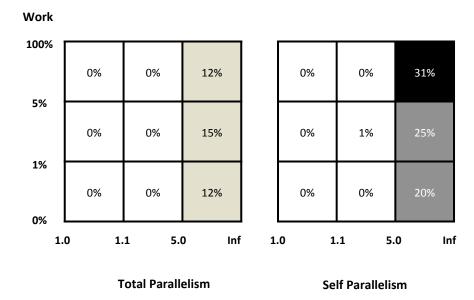

Chapter 4 presents the techniques we developed for planning-aware parallelism discovery. This chapter will first provide background on critical path analysis (CPA), a classic technique for quantifying the amount of parallelism in a program. We will then look at extending CPA to make it useful as part of a practical oracle, culminating with two novel contributions: hierarchical critical path analysis (HCPA) and self-parallelism. HCPA enables analysis of individual regions of a program (e.g. functions and loops), analyzing all regions in only a single pass. Self-parallelism is a new metric that quantifies the amount of parallelism in a program region, excluding the parallelism that comes from regions nested below it. HCPA allows Kremlin to closely approximate self-parallelism without the intractable requirement to store the complete program dependency graph. The results section in this chapter will look at well self-parallelism filters serial regions that would otherwise be considered parallel. We will also look at how well self-parallelism correlates with the regions of a program that were parallelized by third-party experts, showing that self-parallelism matches well with a "ground truth" for parallelizability.

Chapter 5 describes how we can transition from parallelism discovery to parallelism planning. This chapter will begin by describing the problem of parallelism planning both formally and informally. Discussion will then move to two critical components in predicting the result of parallelization: determining which regions contain exploitable types of parallelism and estimating the time of regions

after parallelization. We will then examine how system-specific constraints can be accounted for during planning by introducing the concept of a planning personality. Our discussion will include several proposed planning personalities and the process of developing additional personalities. Results in this chapter will show the effectiveness of Kremlin as a practical oracle. We will look at Kremlin's ability to reduce the number of regions and how that affects the speedup from parallelization. We will also examine Kremlin's ability to accurately prioritize its recommendation, specifically focusing on how much speedup is attainable after implementing a limited percentage of Kremlin's recommendations.

One of Kremlin's main contributions, HCPA, builds upon CPA and is similarly a heavyweight dynamic analysis. This heavyweight nature imposes challenges to the practicality of Kremlin on many systems: high runtime overhead and/or memory overhead could limit Kremlin's utility on all but the highest-end systems. Chapter 6 will look at two separate approaches to limiting both of these types of overhead in HCPA. The first techniques is a novel shadow memory architecture that makes the common case fast and the uncommon cases space-efficient. The second technique utilizes static program analysis to partially evaluate critical paths. Results in this chapter show that the first technique reduces memory overhead—while not greatly increasing runtime overhead—to the point where even standard laptops can evaluate programs using sizable inputs. Results also show that the second technique can significantly reduce the runtime overhead while leaving the memory overhead unchanged.

We will discuss related work in Chapter 7 before summarizing our findings and offering concluding remarks in Chapter 8.

## Acknowledgments

Portions of this research were funded by the US National Science Foundation under CAREER Award 0846152, by NSF Awards 0725357, 0846152, and 1018850, and by a gift from Advanced Micro Devices.

This chapter contain materials from "Kremlin: Rethinking and Rebooting

gprof for the Multicore Age", by Saturnino Garcia, Donghwan Jeon, Chris Louie, and Michael Bedford Taylor, which appears in PLDI '11: Proceedings of the 32nd ACM SIGPLAN conference on Programming language design and implementation. The dissertation author was the primary investigator and author of this paper. This material is copyright ©2011 by the Association for Computing Machinery, Inc.(ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page in print or the first screen in digital media. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or email permissions@acm.org.

# Chapter 2

# The Cost of Inefficient Parallelization

Our introduction described how the process of parallelization was hindered by a lack of tools for several important stages of parallelization, namely parallelism discovery and parallelism planning. In this chapter we will take a look at how the parallelization methodology currently used by many programmers leads is highly inefficient and can lead to poor parallel performance. We will also look at a user study we performed after having developed an early prototype of Kremlin. This user study helped us quantify the impact of inefficient parallelization methodology and provided insight for Kremlin's later designs.

## 2.1 Example Parallelization Methodology

Despite recent research into parallel programming tools, many programmers still rely on a relatively painful methodology that employs serial profiling tools such as **gprof** in order to direct their parallelization activities. The process starts with a serial hotspot list, which ranks regions by the amount of time spent inside them. This list effectively becomes the order that they examine the functions to improve their performance.

It is at this point that the process gets especially onerous. The programmer starts leafing through the code trying to puzzle through the dependencies in the code, and the granularity at which to try to exploit it. Since the programmer has no indication of whether a hotspot is parallelizable, they frequently give up before they are able to recognize subtle but large parallelism opportunities, or they spend excessive amounts of time fruitlessly modifying serial parts of the code. Alternatively, even if parallelism does exist, it may not be large enough to yield speedup, or when combined with lower coverage, the overall speedup may not justify the effort. Finally, interference between nested parallel regions may prevent speedup.

We examined the feature\_tracking benchmark from the San Diego Vision Benchmark Suite (SD-VBS) [KVAJ+09] to illustrate the shortcomings of this coverage-based approach to parallelizing programs. The programmer is typically interested in exploiting either loop-based parallelism (e.g. with OpenMP) or task-based parallelism (e.g. with Cilk++). These types of parallelism require examining the loops and functions in a program so we profiled feature\_tracking to determine the work coverage of its loops and functions. The resulting profile data was then used to sort the loops and functions from largest to smallest coverage.

To demonstrate the lack of correlation between coverage and parallelizability, we manually analyzed the top 20 hotspots in feature\_tracking to determine which of them could be parallelized. Of these top 20 regions, over 50% were either serial (3 functions, 3 loops), contained very limited parallelism (4 functions), or required significant program restructuring to exploit the available parallelism (1 loop). The remaining regions (9 loops) were easily parallelizable, requiring only minor code transformations such as privatization.

Our analysis suggests that relying on gprof or similar profiling tools will lead to less than optimal results. The programmer would be required to analyze a large number of regions that are not parallelizable. This inefficiency results from favoring execution coverage over the other factor in parallelizability: the amount of parallelism available.

While useful, tools that quantify parallelism are alone not quite enough. Rather, parallelization also requires planning tools that help process this information and apply both parallel programming system and machine constraints. With the ability to positively identify the existence of parallelism, and also to prioritize regions, users can invest their time more productively, attacking the correct portions of the program.

## 2.2 User Study

Our own experience with parallelization led us to conclude that current parallelization methodologies—like the one described earlier—are inefficient and can result in poor parallel implementations. This qualitative assessment led us to create an early version of Kremlin that used critical path analysis to quantify the parallelism in every function and loop in the program. This parallelism info was then used to roughly estimate the ideal performance of parallelizing a function or loop and was therefore subsequently used for rudimentary parallelism planning.

We used this early version of Kremlin in a user study that was designed to quantify the impact of parallelism discovery and planning on the parallelization process<sup>1</sup>. More specifically, the user study was designed to answer the following two research questions:

- 1. Would Kremlin users be able to achieve significant speedups sooner than the non-Kremlin users?

- 2. Would Kremlin users spend more time focusing on regions with the largest potential speedup than non-Kremlin users?

In order to answer these questions, we set out to measure both the order in which the participants attempted parallelization and the outcome of their efforts. User study participants included seven graduate students in a parallel architecture course at the University of California, San Diego.

<sup>&</sup>lt;sup>1</sup>This user study was approved by the UC San Diego Institutional Review Board, Project #100056.

#### 2.2.1 Setup

The user study was spread over three class assignments, with each assignment asking them to parallelize one benchmark from SD-VBS using Cilk++. Users were given access to a supercomputing cluster at the San Diego Supercomputer Center where they would have access to AMD computing nodes with up to 32 cores. To ensure a uniform work environment, they were provided with a Makefile system with a small number of commands to control compilation, execution, and debugging of their parallel programs. The result of all commands were logged so that we could accurately retrace the steps they took. After each run of their program, a snapshot of their code was saved so that we could recreate the changes they made as they worked on the assignments.

Both of our research questions relied on knowledge of the time spent on various tasks; accurate accounting of time was therefore of the utmost importance. For each command the participants ran, users were asked to enter in the amount of time they had spent actively working on the assignment since they last reported. Using this data, we could determine how long they spent on each task. It is well-known that self-reported data can be inaccurate so we did not rely solely on this data for recreating the time spent on each task. We instead bolstered the self-reported data by incorporating some automatic data that was available from the logging we did with each command. This hybrid approach is similar to the one described in [HBZ<sup>+</sup>05]. To further increase our understanding of their efforts, we also prompted users to optionally describe their work activities since their last reported time.

The study was split across three class assignments. The first assignment acted as a primer for parallel programming using Cilk++ and for using the parallel programming environment we created. The students were given an hour-long demonstration of how to use our programming environment as well an introduction to using Cilk++ for parallelization. The students were also given a tutorial on effectively using Kremlin before their first required use of the tool.

We split students into two groups, groups A and B, for the final two assignments: one with access to the early Kremlin prototype and another without

access. The group without access to Kremlin was the control group that allowed us to factor out the variation in difficulty of parallelizing across the different programs. The control group switched between the assignments two and three: group A was the control for assignment two while group B was the control for the assignment 3. Both groups were given access to gprof as a tool to help them plan for which regions to parallelize.

We formed the two groups in the following way. At the end of the first assignment we analyzed the users' logged data for the amount of time spent and the speedup achieved. We used this data to compute a performance-to-work ratio, which we used to rank each student's performance. We used this ranking to split the students into two groups of roughly equal skill.

#### 2.2.2 Benchmark Analysis

Before looking at the results of the user study, we will analyze each of the three benchmarks in detail to identify the regions that were the most critical in achieving the best parallel implementation.

We parallelized the programs to get a reference version with the best speedup, and noted which functions and loops were required to be parallelized in this optimal implementation. We refer to these regions as the "critical" regions. The benchmarks were of limited size, allowing us to be confident that we had achieved the best speedup possible. After gathering the results, we checked the students' implementations for any possible speedups that we missed in the reference implementation but did not find any.

Table 2.1 details the regions that were found to be critical for each program. Also given in this table is the speedup that could be achieved by parallelizing this region and any that are listed above it for that program. This number formed a bound on what we believe to be the best speedup attainable using only parallel programming transformations.

**Disparity** Disparity was the first benchmark that was assigned and was also the simplest to understand, containing less than 500 lines of code. Based on our

Table 2.1: **Speedup and Recommendation Rank of Critical Regions.** Critical regions were those regions found to be essential in obtaining maximum parallel performance. These regions were not the only ones that benefited from parallelization but parallelizing other regions in addition to these would not lead to higher speedups. Also shown are the order in which these regions were recommended by the early Kremlin prototype and **gprof** (based on both self- and total-time).

|           |                                   |         | Recommendation Rank |           |            |  |  |  |  |  |

|-----------|-----------------------------------|---------|---------------------|-----------|------------|--|--|--|--|--|

|           |                                   |         |                     | gprof     | gprof      |  |  |  |  |  |

| Benchmark | Function                          | Speedup | Kremlin             | self-time | total-time |  |  |  |  |  |

| disparity | getDisparity                      | 3.5     | 1                   | 14        | 2          |  |  |  |  |  |

|           | $\operatorname{script\_tracking}$ | 1.3     | 1                   | NA        | 1          |  |  |  |  |  |

| tracking  | calcPyrLKTrack                    | 1.2     | 5                   | 14        | 4          |  |  |  |  |  |

|           | calcGoodFeature                   | 2.1     | 4,10                | 17        | 10         |  |  |  |  |  |

|           | imsmooth                          | 4.1     | 1,2                 | 1         | 4          |  |  |  |  |  |

| sift      | $\operatorname{sift}$             | 6.4     | 3                   | 2         | 2          |  |  |  |  |  |

| SIIL      | fSetArray                         | 8.4     | 5                   | 4         | 6          |  |  |  |  |  |

|           | diffss                            | 10.1    | 4                   | 3         | 5          |  |  |  |  |  |

analysis we found that parallelizing a single function, getDisparity, was enough to achieve the best speedup available. getDisparity consisted of a loop where the image disparity was found at many different levels. The disparity in each iteration could be calculated independently of the other iterations and thus most of the work in the loop could be done in parallel. However, at the end of each iteration, the current disparity value was checked against the best value so far. The loop could be parallelized with modest effort by privatizing the intermediate disparity arrays and distributing the comparison into another (sequential) loop afterwards.

Scale-Invariant Feature Transform (SIFT) Our analysis determined the four most important regions in the SIFT program to be imsmooth, sift, fSetArray, and diffss. The imsmooth function contained two loops which were easily parallelized with the  $cilk\_for$  primitive but which could achieve a speedup of over  $4\times$ . The fSetArray and diffss functions had a similar format and difficulty but only one of the loops was important for performance. The sift function, although offering ample potential speedup was much harder to parallelize.

Feature Tracking For the feature tracking algorithm, we identified three critical functions: script\_tracking, calcPyrLKTrack, and calcGoodFeature. The for loop in the script\_tracking function processed each frame based on the previous frame's output. Thus, it had a strong sequential component. However, each image is preprocessed before the features are located. This preprocessing step could be done in parallel for all images since it does not depend on previous images. Refactoring the code such that the preprocessing occurred before the main for loop therefore offered a significant potential speedup (1.36×). Identifying and refactoring the main for loop was a non-trivial task with only three students successfully accomplishing this task.

The loop in the calcPyrLKTrack function offered similar speedup potential but involved much easier code transformations. To successfully parallelize this loop, several variables needed to be privatized. All but one of the students was able to successfully parallelize this region.

Finally, the calcGoodFeature function also offered a significant potential speedup—albeit much smaller than script\_tracking or calcPyrLKTrack. This function was trivially parallelizable, requiring the addition of only two cilk\_for keywords to the loops in the function.

## 2.2.3 Impact on Program Speedup

One of the questions we wished to answer was if access to Kremlin would effect the speedups obtained by the user. We might expect access to the tools to have one or both of the following effects:

- 1. Improved performance at the end of the parallelizing process.

- 2. Decreased time required to obtain the largest possible speedup.

To test whether the final performance improved as a result of using Kremlin, we tabulated the final speedup time for all users and calculated the average value for Kremlin users and the average for non-Kremlin users. Table 2.2 shows this result. While the Kremlin users had slightly better performance than non-users

Table 2.2: **Speedup Achieved and Time Spent.** Kremlin did not have a strong impact on the final speedup obtained by the participants: **tracking** was nearly the same (1.8 with Kremlin, 1.7 without), while **sift** had a significant difference (7.2 with, 9.2 without) due mostly to the lack of effort (and subsequent poor performance) of user 139. The lack of difference can also be explained by the limited complexity of the benchmarks compared with the time given to parallelize them.

|             | tracki  | ng    | sift    |       |

|-------------|---------|-------|---------|-------|

| User        | Speedup | Time  | Speedup | Time  |

| 139         | 1.6     | 235   | 2.4     | 88    |

| 280         | 2.3     | 1195  | 7.8     | 279   |

| 579         | 1.2     | 176   | 6.9     | 274   |

| 911         | 1.6     | 405   | 11.5    | 375   |

| 143         | 2.2     | 602   | 7.4     | 184   |

| 249         | 1.6     | 528   | 11.4    | 401   |

| 371         | 1.4     | 737   | 8.7     | 297   |

| Kremlin     | 1.8     | 622.3 | 7.2     | 254   |

| non-Kremlin | 1.7     | 502.7 | 9.2     | 294   |

| Average     | 1.7     | 554   | 8.0     | 271.1 |

for tracking, the difference (1.8 vs 1.7) was not significant considering the small sample size. In sift, the average for Kremlin users is well below that of the non-users (7.2 vs 9.2) but performance of user 139 was clearly an outlier that skewed the average. The average excluding this user rises to 8.8, but the difference is still too small lead to conclusive results.

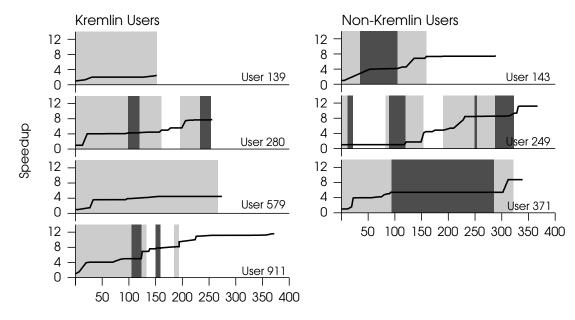

To determine if Kremlin was able to decrease the time required to obtain the maximum speedup, we looked at each users speedup as a function of the amount of time they worked. If Kremlin did make an impact, we would expect the slope of Kremlin users to be larger than that of non-Kremlin users. Figure 2.1 shows the speedup vs time graphs for each of the users on the sift benchmark. Also indicated in this figure is the time spent parallelizing critical regions (light gray), time spent on non-critical regions (dark gray) and time spent on sequential optimization (white). The top 4 users (139, 280, 579, and 911) were Kremlin users. While there is no clear trend on the slopes of Kremlin vs non-Kremlin, it

Time Spent (Minutes)

Figure 2.1: Speedup vs Time Graphs (sift). The graphs show the speedup obtained by each user as a function of the amount of time spent. Also shown is a breakdown of the periods of time spent on different types of regions; light gray indicates time spent in critical regions, dark gray indicates time spent in non-critical regions, and while indicates time spent doing serial optimization. The graphs indicate that Kremlin users spent much more of their time parallelizing critical regions than the non-Kremlin users.

is clear to see that the times were spent very differently between the two groups. Kremlin users had much more time in the critical regions (gray) than the others. Unfortunately the time spent in the regions does not seem to indicate the end success of the parallelization efforts or we would have seen a clearly steeper slope for Kremlin users.

#### 2.2.4 Time Spent On Critical Regions

The other question which we wished to answer with the user study was whether Kremlin would direct users to spend more time working on parallelizing regions that offered the most speedup (i.e. the critical regions). To answer this question, we looked at the amount of time spent working on each function and calculated the percentage of this time that was spent working on critical regions.

Table 2.3: **Time Spent (%) Parallelizing Critical Regions.** The average time spent working on parallelizing "critical" regions greatly differed between Kremlin and non-Kremlin users. The Kremlin group spent an average of 83.9% (group A) and 83.6% (group B) of their time working in critical regions on the **tracking** and sift benchmarks, respective. This number dropped to 48.6% and 51.8% for the group without access to Kremlin.

|           |                             | % Time Spent (Avg.) |         |

|-----------|-----------------------------|---------------------|---------|

| Benchmark | Benchmark   Critical Region |                     | Group B |

| disparity | getDisparity                | 18.5                | 21.2    |

| tracking  | script_tracking             | 55.4                | 23.9    |

|           | calcPyrLKTrack              | 26.7                | 18.5    |

|           | calcGoodFeature             | 1.7                 | 6.1     |

|           | Total                       | 83.9                | 48.7    |

| sift      | imsmooth                    | 12.0                | 29.4    |

|           | sift                        | 30.3                | 41.5    |

|           | fSetArray                   | 2.4                 | 3.2     |

|           | diffss                      | 7.0                 | 13.5    |

|           | Total                       | 51.9                | 87.7    |

Based on the quality of Kremlin's recommendations in Table 2.1 and its ability to predict speedup we know that Kremlin users had a good idea of what were the critical regions. We can therefore hypothesize that Kremlin users will show a clear advantage in the percentage of time spent working on critical regions.

Table 2.3 overviews the percentage of time each group spent working on each of the "critical" regions as well as the total time spent across all of these regions. To control for the variation caused by the time users worked on serial optimization rather than parallelization, we did not include the time spent doing serial optimization in the total time spent. Across both assignments, non-Kremlin users spent approximately 50% of their time working on the critical regions (48.7% and 51.9% for tracking and sift, respectively). In contrast, Kremlin users spent roughly 85% of their time working on these critical regions (83.9% and 87.7% for tracking and sift). This clearly shows that Kremlin was able to focus users on the regions that mattered most and is strong evidence for our hypothesis.

#### 2.2.5 Threats to Validity

Having discussed the results of our user study, we will now examine how we addressed threats to the validity of our findings. In particular, we were concerned with threats to three types of validity: construct validity, internal validity, and external validity. Construct validity concerns whether our hypotheses are the best explanation of the results. Internal validity concerns whether the independent variables are responsible for the changes in the dependent variables. External validity concerns whether our results apply to a broader population than those involved in the study.

Construct Validity We faced one major threat to construct validity in this study. We needed to ensure that the speedup measured was the speedup obtained from parallelization and not from some other optimization. In the first two assignments we did not advise the participants against doing serial optimization and therefore several students achieved significant program speedup from serial optimization. In the third assignment we instructed the students to focus on parallel optimization as their grades would depend on that aspect of their speedup. However, as there was common code shared among the three programs used, some students used their old serial optimization on the final assignment. We controlled for this in two ways: we factored out the sequential time when calculating the percentage of time spent in critical regions; and we clearly labeled time spent on activities other than parallelization in the individual speedup vs. time graphs.

Internal Validity One possible threat to the internal validity of our study was misuse of the planner. Based on written reports and logged data, we found that some students did not use the tool as we had intended. In general, we found several major ways in which they deviated. First, because there was some code reuse between assignments, some students spent time re-implementing the same changes they had made in previous assignments. Often this meant that they optimized regions that were either not recommended or were only weakly recommended by the Kremlin. Another common way in which they deviated was by favoring gprof

results over Kremlin. gprof orders functions by the time spent inside of them. This was often misleading though as either the parallelism was too low in these functions or the parallelism was too fine-grained and did not offer significant performance gains. Finally, some students seemed to favor parallelizing on a first come, first serve basis. As a result, some students tried parallelizing functions that were called from the main function because those were the first they encountered. As a result of these deviations, we could not successfully test our initial hypothesis that Kremlin users would achieve significant speedups faster than non-Kremlin users.

**External Validity** One threat to the external validity of our study was the complexity of the programs that were parallelized in the study. These programs had a relatively small amount of code (less than 1000 lines of code) spread across 10-15 source files. A significant portion of the files had the same basic structure: two DOALL loops with one level of nesting each. Furthermore, several of these files were common files that were reused across the three assignments. This worked to limit the areas in which the students had to look for parallelism opportunities. The eight days given for each assignment was ample time for them to identify the major opportunities for exploiting parallelism. As a result of the limited complexity of these programs and the time they had to work on them, we did not expect Kremlin users to have significantly better performance than non-Kremlin users. However, we expect that Kremlin will have a more noticeable impact on more complex applications as its ability to focus users on the most critical regions becomes more important. Other threats to external validity include the limited parallel programming background of the participants and the lack of more sophisticated parallel performance measurement tools to help determine bottlenecks in performance.

#### 2.2.6 Conclusions

While we were unable to show that the early Kremlin prototype was able to reduce the time needed to parallelize a program, our results indicate that users benefited from have a parallelism planner. To understand the strengths and weaknesses of early Kremlin prototype, we asked for qualitative feedback from the users in the form of a survey of short answers. The combination of quantitative and qualitative feedback was able to provide us valuable insight that we would carry forward into Kremlin's later designs.

We noticed that despite having a planner, study participants often chose to ignore its advice. Students indicated that they were often unable to quickly determine the "trick" to successfully parallelizing a recommended region; when a recommendation looked too difficult to quickly parallelize, they simply moved on to a region that they thought we be easier. This initial confusion about how to parallelism was likely a direct result of a lack of guidance about the type of parallelism available in a region. The type of transformations needed to exploit parallelism is often directly tied to the type of parallelism. For example, DOALL parallelism in loops commonly require privatization of variables to eliminate false dependencies and loop fission to remove serial parts of a loop.

Student participants had access to parallelism charts to help determine the type of parallelism but student surveys indicated that they did not find them very useful overall. The deficiencies found in parallelism charts led us to re-examine our parallelism metrics, prompting the eventual creation of the new *self-parallelism metric* and techniques to help identify the type of parallelism. We will discuss the strengths and weaknesses of parallelism charts in Section 4.4.1, contrasting them with the self-parallelism metric described in Section 4.4.2. Section 5.3 discusses how later versions of Kremlin can identify the type of parallelism in a region.

We also noticed that students would occasionally continue working on a region even after obtaining the maximum possible speedup for that region. This likely resulted from the confusion caused by the rudimentary speedup estimates in the early Kremlin prototype. We addressed this shortfall partially through the creation of the self-parallelism metric and an improved parallel time estimation model, but also through the introduction of *planning personalities*. Planning personalities allow for tailor the planner to the specifics of a target machine and greatly enhance the quality of plans. Section 5.2 discusses our more advanced model of parallel execution time while Section 5.4 discusses planning personalities and describes several we have created.

#### Acknowledgments

Portions of this research were funded by the US National Science Foundation under CAREER Award 0846152, by NSF Awards 0725357, 0846152, and 1018850, and by a gift from Advanced Micro Devices.

This chapter contain materials from "Kremlin: Rethinking and Rebooting gprof for the Multicore Age", by Saturnino Garcia, Donghwan Jeon, Christopher Louie, and Michael Bedford Taylor, which appears in *PLDI '11: Proceedings of the 32nd ACM SIGPLAN conference on Programming language design and implementation.* The dissertation author was the primary investigator and author of this paper. This material is copyright ©2011 by the Association for Computing Machinery, Inc.(ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page in print or the first screen in digital media. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or email permissions@acm.org.

## Chapter 3

# System Overview

Kremlin is designed to be a practical oracle for sequential code parallelization. To be considered practical, Kremlin must be both simple to use and accurate, guiding programmers to the most important parts of the program with as little manual intervention as possible.

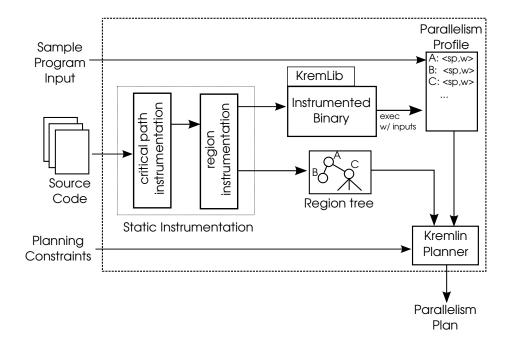

In this chapter we will look at Kremlin's basic usage model and the underlying system architecture that supports this model. Kremlin's system architecture introduces several new techniques, including hierarchical critical path analysis (HCPA), self-parallelism, and planning personalities. These techniques will be introduced in this chapter to provide insight into their interrelations, but detailed descriptions of these techniques and their implementations will be delayed until subsequent chapters.

#### 3.1 Usage Model

Kremlin's user interface presents a simple three step usage model for obtaining a parallelization plan. Kremlin's usage model takes inspiration from gprof, with simplicity and clarity of results paramount. Figure 3.1 demonstrates this usage model. Kremlin starts with unmodified, serial source code and produces an instrumented binary. The user then runs this binary with its normal inputs to produce a dynamic parallelism profile. This profile is used by Kremlin's parallelism planner, along with a specified planning personality (OpenMP in the example), to

```

$> make CC=kremlin-cc

$> ./srad 100 0.5 502 458 image.pgm

$> kremlin srad --model=openmp --num_cores=4

Cores